KNOWLEDGE SHARE

Knowledge Share è una piattaforma dedicata alla valorizzazione della Ricerca Pubblica nazionale il cui obiettivo è quello di mettere in contatto i team di ricerca con aziende ed investitori.

Scopri le Start-up dell'ecosistemaPartner di progetto

Trending Sectors

Una selezione di tecnologie e progetti che toccano settori ed applicazioni maggiormente all'avanguardia nell'ecosistema dell'innovazione attuale, a rotazione.

Nuovi brevetti disponibili

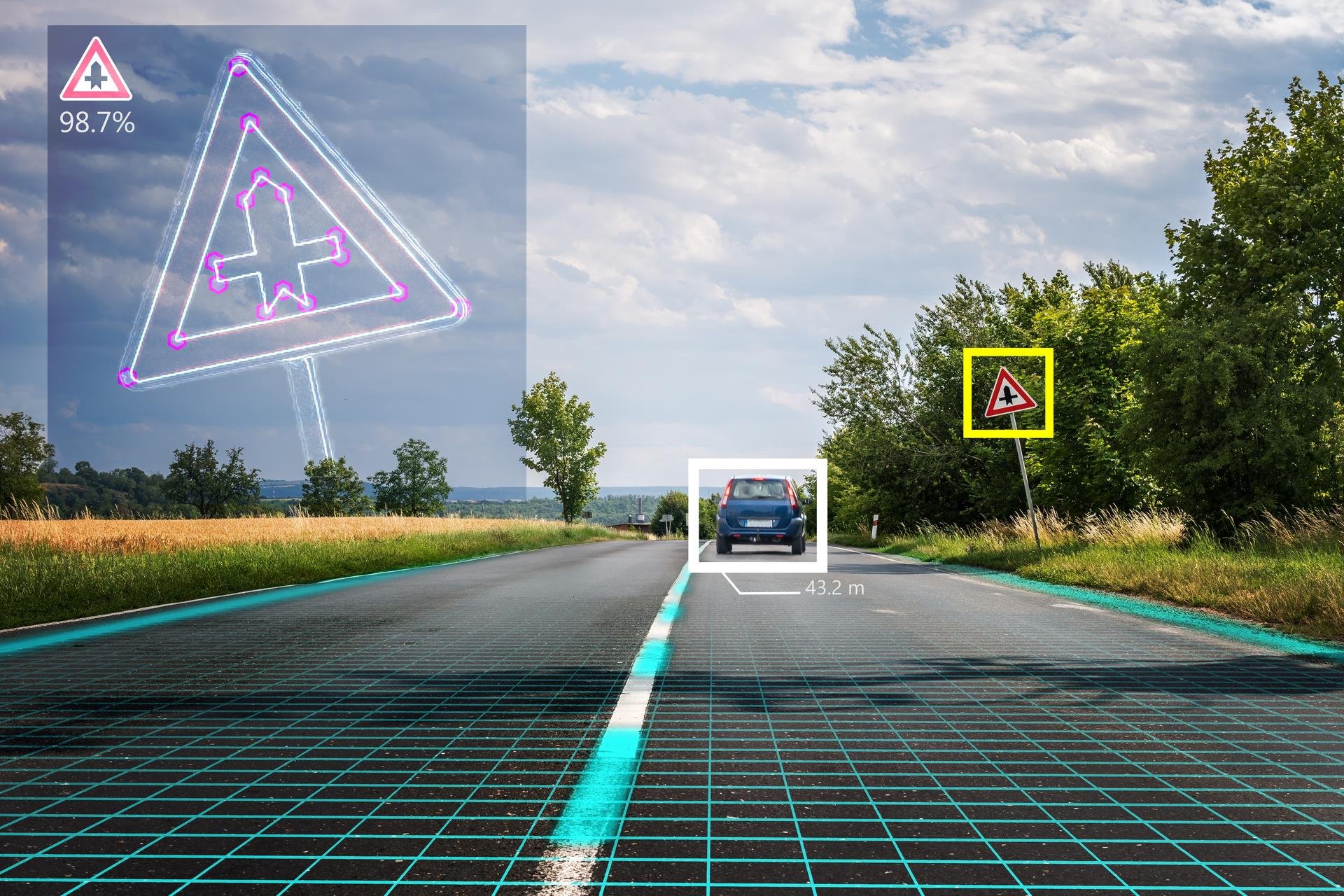

SEM-O-RAN: Semantic NextG O-RAN Slicing

Connettività & Telecomunicazioni | Enhanced Edge Computing | Mobility - Veicoli Interconnessi

SEM-O-RAN è un framework di network slicing per reti mobili di nuova generazione in grado di orchestrare l’offloading di task di Machine Learning all'Edge.

TRL

Necessità di finanziamento

Looking for

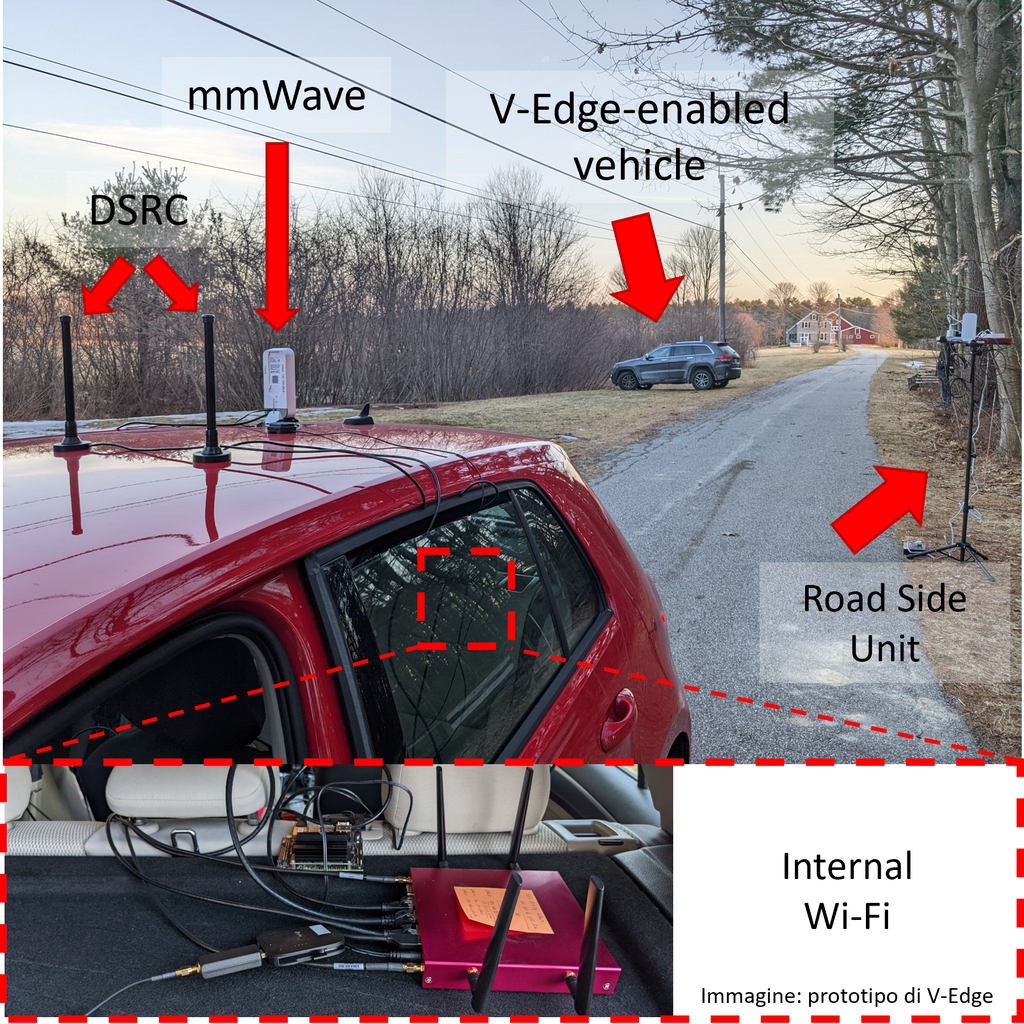

V-Edge: Vehicular Enabling Edge Intelligence

Comunicazioni | Connettività & Telecomunicazioni | Mobility - Veicoli Interconnessi

V-Edge è un framework innovativo per reti e comunicazioni veicolari, focalizzato alla “Vehicular Edge Intelligence” (VEI): intelligenza artificiale e casi d'uso avanzati a bordo veicolo e all'edge della rete.

TRL

Necessità di finanziamento

Looking for

RETICOLANTI LIQUIDI A BASE DI ESTERI BORONICI PER TERMOINDURENTI A BASE EPOSSIDICA

Materiali Avanzati - Nanomateriali

I vitrimeri combinano le caratteristiche dei termoplastici e termoindurenti. Con esteri boronici, sostituiscono i termoindurenti nei compositi. Scopo: sviluppare reticolanti dinamici per curing di epossidi a basse temperature.

TRL

Looking for

Le ultime notizie dall'ecosistema

10 aprile 2024

Netval e Knowledge Share: insieme al WMF - We Make Future come partner dell’evento.

Scopri di più

29 marzo 2024

“Detector con finestre ottiche micrometriche”: la tecnologia dell’INFN che impatta sul monitoraggio di rivelazione delle particelle. Intervista a Nicolò Cartiglia.

Scopri di più

28 marzo 2024

IntelligEarth: proteggere il patrimonio ambientale e culturale con gesti quotidiani e alla portata di tutti

Scopri di piùNuove Start-up disponibili

Spritz Matter

Decision Intelligence

Spritz Matter aiuta le aziende medie e grandi a migliorare la loro Cybersecurity posture. Unisce approcci tradizionali e strumenti di avanguardia, per accompagnare le imprese nei loro processi di innovazione di servizi e prodotti, offrendo servizi taylor-made.

TRL

Fase di finanziamento

Looking for

iBMB - initiatives for Bio-Materials Behaviour

Green Chemistry | Medicina Preventiva E Diagnostica | Servizi Di Consulenza (Multi-Settoriali)

iBMB sviluppa strumenti per prevedere la progressione dei tumori e la risposta a nuovi trattamenti, mirati a terapie personalizzate per i pazienti affetti da cancro. Ad oggi ha elaborato 3 prodotti rivoluzionari: CancerMate, TASCairfoils, SHRIMPAK.

TRL

Fase di finanziamento

Looking for

Nutribiofoods

Alimenti & Bevande - Processi | Food As A Medicine | Nuovi Prodotti

La società offre servizi di consulenza scientifica nelle attività connesse alla prototipazione di alimenti funzionali mediante l'utilizzo di composti bioattivi naturali o derivanti del metabolismo microbico.

TRL

Fase di finanziamento

Looking for

Tech Collider - "A Knowledge Share Event"

Il TECH COLLIDER - "a Knowledge Share event" rappresenta un evento internazionale gratuito che ha l’obiettivo di mettere in contatto esperti ed opinion leader dall’accademia, dal mondo dell’industria e da quello degli innovatori, per promuovere la collaborazione e stimolare la creazione di sinergie.